SiC物理气相传输法(PVT)的掺杂以及测试

按照掺杂后电阻率来分类,碳化硅衬底主要有导通型衬底和半绝缘衬底两种。导通型碳化硅衬底具有低电阻率,特别适合垂直型功率器件的制造用来降低串联电阻,而减少功率损耗。而半绝缘衬底具有较高电阻率,多用于横向高频器件制造中,用来减小寄生阻抗,因此在5G通讯和新一代智能互联、器件上具备广阔的应用空间。以下我们针对这两种衬底材料分别介绍。

导通型SiC衬底

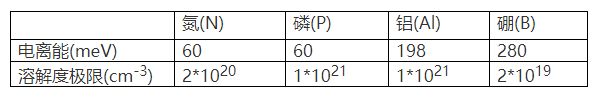

导通型衬底又可以分为N型和P型。和Si材料类似,N型掺杂可以使用Ⅴ族元素来实现,使用Ⅲ族元素来实现P型掺杂。表1列出了氮、磷、铝、硼四种元素在4H-SiC晶体中的电离能和溶解度极限。从溶解度极限来看,四种材料都可以实现大于e19的重掺杂。而从电离能来看,硼元素的电离能最高达到了280meV,而我们知道掺杂元素的电离化率是和电离能成反比关系,所以相同掺杂条件下硼元素的电离化率最低。除此以外,在高温条件下,硼元素会发生异常高的扩散而改变掺杂结构分布,所以实际生产中很少使用硼元素作为P型掺杂元素,而常用铝元素作为首选。N型掺杂中,氮和磷元素都可以用做掺杂元素,实际生产中大多用氮元素作为首选。(四川半导体设备)

P型掺杂工艺实现上要难于N型掺杂。一般在PVT坩埚内加入铝化合物(Al4C3)来升华产生铝蒸汽,通过控制铝蒸汽的分压来控制铝的掺杂浓度。但是在生长过程中铝源耗尽现象很难控制,同时重掺杂铝源也会改变坩埚内的生长环境,会优先生长出6H-SiC,即使籽晶用的是4H-SiC,多型体控制也非常困难。所以常见P型4H-SiC晶圆的掺杂浓度和电阻率分别为0.5~2x1018cm-3和1~5Ω·cm,更低的电阻率晶圆需要特殊工艺来得到。

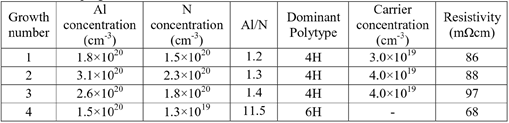

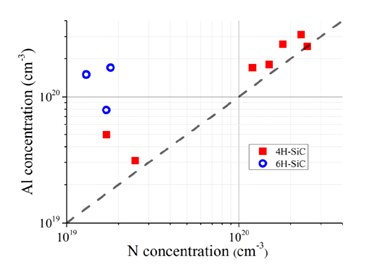

近来报道有日本团队使用铝和氮共掺杂技术,可以实现铝的重掺杂[4]。他们分别使用Al4C3和氮气作为P型和N型的掺杂源,使用了2寸的4H-SiC作为籽晶,在2050-2200℃温度下,通过调节铝蒸汽和氮气的分压比,可以实现铝的重掺杂而且也能抑制6H-SiC多型体的产生。他们分别使用SIMS测试了铝和氮的含量;涡流法测试了电阻率;拉曼光谱法测试了多型体。表2是测试结果汇总,我们可以看出为了得到铝重掺杂的4H-SiC晶体,需要控制Al/N掺杂比例略大于1,该方法得到的最小P型掺杂电阻率为0.086Ω·cm。图3是该团队尝试不同Al/N掺杂比下,制备得到的晶体多型体测试图,可以看出来4H-SiC更容易在Al/N掺杂比为1的环境下生长,偏离了该比例很容易生产出6H-SiC晶体。(四川半导体微组装清洗设备)

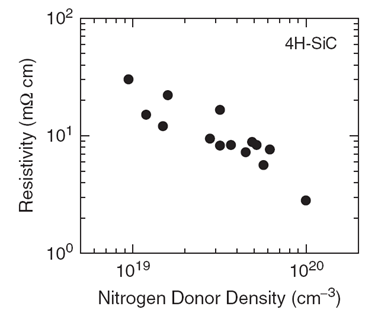

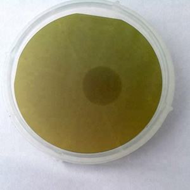

电阻率是掺杂工艺最关注的参数,电阻率的均匀性也是衡量拉晶工艺的重要指标。在实际生产过程中,电阻率的分布经常表现为径向上电阻率中间低、边缘高;而晶锭沿轴向上电阻率生长前期低、后期高的特征。我们以常见的N型4英寸SiC晶圆为例(图4.),经常可以观察到中间区域颜色有别于其他区域。这是因为碳化硅在掺杂后发生了导带载流子吸收现象,N型SiC导带吸收波长为460nm, 光的吸收率是和掺杂浓度正相关的。中间区域的掺杂浓度高于其他区域,表现在了衬底颜色不一致。

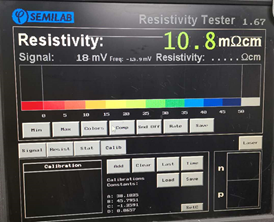

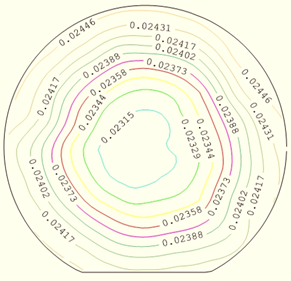

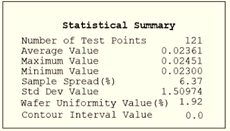

在晶锭切片和抛光工艺后,加工成的晶圆电阻率测试也是必不可少的。目前市场上最常用的测试设备是Lehighton公司的LEI1500[5]。该设备使用涡流法在去边仅为7mm的晶圆范围内可对预设点位进行无接触测试,图5为测试结束后生成的晶圆电阻率map图以及数据统计值。

半绝缘SiC衬底具有较高电阻率,可以在高频器件制造中减小寄生阻抗,因此在5G通讯和新一代智能互联器件上具备广阔的应用空间。同时考虑到它与GaN材料的低晶格失配率和超高的热导率,该衬底也是 GaN 异质外延的优选材料。

PVT法生长SiC单晶过程中,由于SiC原料粉末和石墨坩埚含有大量杂质,限制了半绝缘衬底的生长。典型的金属杂质有Ti, V, Cr, Fe, Co, Ni等,浓度在1013-1015cm-3量级。此外,N和B等杂质也会包含在晶锭中,浓度范围也在1013-1015cm-3量级,所以即使非故意掺杂,生长的晶锭或者是N型或者是P型。理论上,如果可以控制这些杂质的浓度到1010cm-3量级以下,就可以得到半绝缘型衬底[1]。但是实际生产中,SiC原料粉末、生长设备以及操作环境无法达到这一要求,所以目前制作半绝缘型衬底是通过深能级补偿办法来实现的。根据具体工艺不同,可以分为如下两类:1)外界引入化学杂质,产生深能级的陷阱中心,来降低载流子浓度,该方法被称为掺杂半绝缘。2)利用本征点缺陷作为深能级中心来补偿浅能级杂质,该方法被称为高纯半绝缘。下面我们分别单独介绍这两种方法。

掺杂半绝缘方法常用的化学杂质为金属钒。因为它是两性杂质,所以既可以用来P型掺杂也可以用来N型掺杂。对于钒引入的深能级,在N型掺杂中,它的位置位于导带下0.9eV处;在P型掺杂中,它的深能级位置位于价带上1.4eV处。因为4H-SiC能带宽度为3.2eV,所以对于两种掺杂钒都可以形成深能级,从而把费米能级限制在深能级左右,这样就降低能带中的自由载流子浓度。通过该方法,可以得到电阻率大于1012Ω·cm半绝缘衬底。

高纯半绝缘方法,是利用本征点缺陷作为深能级中心来补偿浅能级杂质来实现的。本征点缺陷主要包括如下:硅空位缺陷;碳空位缺陷;硅空位-碳空位的双空位缺陷。本征点的缺陷可以通过PVT生长工艺进行控制,也可以通过高能粒子辐射工艺来改变本征点缺陷。该方法也可以得到电阻率为1012Ω·cm量级的半绝缘衬底。

半绝缘SiC衬底的电阻率可以高达1012Ω·cm量级,电阻率检测也是一个巨大挑战,涡流法已经不再适合,现在多用电容充放电法来进行测试。图6所示是4”半绝缘4H-SiC晶片。因为不存在浅能级引起的载流子特征吸收,所以相较于N型重掺杂晶圆的琥珀色,它一般为无色。

图6. 4”半绝缘4H-SiC晶片

更多的四川半导体微组装设备资讯请联系:18980821008(张生)19382102018(冯小姐)

四川省微电瑞芯科技有限公司http://www.wdrx-semi.com/