本文回顾了光学光刻、极紫外光刻技术。讨论了这些技术的演变过程及其在设备制造中的应用。此外,还讨论了过去十年中为提高这些设备的分辨率而开发的不同曝光工具、化学放大和非化学放大光刻胶、掩膜和无掩膜光刻技术及其优缺点。(四川半导体微组装设备公司)

1.导言

Pease, R.F.; Chou, S.Y. Lithography and Other Patterning Techniques for Future Electronics. Proc. IEEE 2008

1 Ko, W.H. Trends and frontiers of MEMS. Sens. Actuators A Phys. 2007

2 Ming, L. Electron beam lithography and its application in fabricating nano-device 2004

3 The application of EUV lithography for 40 nm node DRAM device and beyond. 2009

在半导体基板上,通过各种工艺制作出芯片,然后将芯片连线形成集成电路(IC)。据估计,光刻技术约占芯片制造成本的30%,因此是集成电路制造的主要部分。随着芯片密度的不断提高,这项技术成为缩小设备尺寸的技术限制。

1Altissimo, M. E-beam lithography for micro-/nanofabrication. Biomicrofluidics 2010

2 Ion Beam Lithography and Nanofabrication: A Review. Int. J. Nanosci. 2005

光刻技术的一些常见组成部分包括光学系统、光刻胶、掩膜和对准标记。光学系统由透镜、光源、光探测器、图像平面等组成。光刻模拟器可用于研究和优化各种照明和镜头条件。

1 Ito, H. Advances in Chemical Amplification Resist Systems. Jpn. J. Appl. Phys. 1992

2 Laminated dry film resist for microengineering applications. Microelectron. Eng. 1996

1 Optimization of Segmented Alignment Marks for Advanced Semiconductor Fabrication Processes; Sullivan, N.T., Ed.; SPIE: Bellingham, WA, USA, 2001

2 New alignment mark designs in single patterning and self-aligned double patterning. 2017,

3 Front-to-Back Alignment Metrology; Engelstad, R.L., Ed.; SPIE: Bellingham, WA, USA, 2003

1 Integration of New Alignment Mark Designs in Dual Inlaid Copper Interconnect Processes.2002

Conjugate Twin-Shifter for the New Phase Shift Method to High Resolution Lithography. Proc. SPIE 1991

1 New Approaches to Nanofabrication: Molding, Printing, and Other Techniques. Chem. Rev. 2005,

2 Progress of the EUVL alpha tool. In Emerging Lithographic Technologies V; SPIE: Bellingham, WA, USA, 2001

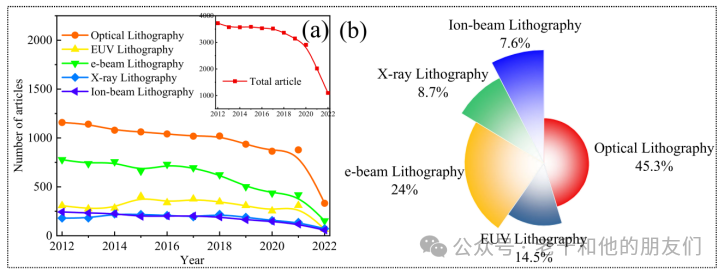

过去几十年中,人们在光刻技术方面做了大量工作。图 1a 显示了过去十年中光刻技术和各种光刻技术的发展趋势。图 1b 描述了过去五年中各种光刻技术的占比。

图 1:(a) 光刻技术及其各种技术的发展趋势;(b) 过去五年中不同光刻技术的占比[数据来源:Scopus]。

这些数据表明,半导体行业对光刻技术的需求仍在继续。与先进光刻技术的发展相反,光学光刻技术的发展仍处于领先地位。最近几年,光刻技术的工作有所减少,因为新的数字技术正在发展,可以在短时间内实现锐利、精确的图案化,用于制造纳米级设备。随着纳米压印光刻技术、相干光刻技术、原子层沉积光刻技术、光子上转换光刻技术和基于化学的直接自组装(DSA)等新光刻技术的发展,对光学光刻技术和其他传统技术的需求也在减少。

在不同的光刻技术中,光学光刻技术、极紫外光刻技术、电子束光刻技术、X 射线光刻技术和离子束光刻技术属于传统光刻技术。这些技术在图案化工艺流程方面也很相似。

2.光学光刻(四川半导体设备清洗设备)

1 Room-temperature operation of silicon single-electron transistor fabricated using optical lithography. IEEE Trans. Nanotechnol. 2011

2 Graphene nanopatterning by Quantum Optical Lithography. Optik 2020

3 Fabrication of Efficient Single-Emitter Plasmonic Patch Antennas by Deterministic In Situ Optical Lithography using Spatially Modulated Light. Adv. Mater. 2022

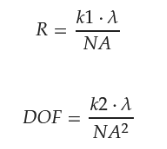

光学光刻技术之所以被广泛使用,直接原因在于其高度并行的特性,可以在极短的时间内传输大量信息。在光学光刻技术中,大量芯片是一次性制造的,因此它是一种省时、快速的生产技术,而且制造成本较低。在集成电路制造中,使用紫外光(0.2-0.4微米)或深紫外光的光学光刻技术应用最为广泛。在光学光刻技术中,超小型图案被印制在晶片上,以制作复杂的集成电路。

图 2. 光学光刻原理图

Okazaki, S. High resolution optical lithography or high throughput electron beam lithography: The technical struggle from the micro to the nano-fabrication evolution. Microelectron. Eng. 2015

第一个商用还原曝光系统是DSW(晶圆直接步进)。在步进系统的早期阶段,使用波长为436 nm的高压汞灯g线源。1970年代,NA为0.28,分辨率为1微米。20 世纪80年代中期,NA提高到0.5。但NA值越高,焦深损失越快。20 世纪80年代末,在g线(436 纳米)之后引入了i线(365 纳米)曝光。此外,还尝试引入KrF准分子激光器(193 纳米)。

M. Dubroecq博士于1982年推出了基于准分子激光的曝光系统,V. Pol博士于1986年推出了全场步进机。g线和I线的投影光学系统非常相似,这有助于I线缩减曝光系统的开发。KrF激光的投影光学与g线有很大不同。KrF准分子激光器需要石英材料的透镜。但半导体行业对高分辨率的需求仍在继续。在F2激光器的帮助下,尝试将曝光波长从193 nm减少到157 nm。但是它需要一套新的曝光工具、抗蚀剂材料和掩模材料,因此这一尝试失败了。然后,浸没式光刻技术被引入,通过降低波长来实现高分辨率。

Owa, S.; Nagasaka, H. Immersion Lithography; Its Potential Performance and Issues; Yen, A., Ed.; SPIE: Bellingham, WA, USA, 2003

2.1 曝光系统

Automated Optical Proximity Correction: A Rules-Based Approach; Brunner, T.A., Ed.; SPIE: Bellingham, WA, USA, 1994

2.2 光刻胶

光刻胶也叫光致抗蚀剂,是一种光敏材料,在光线照射下会聚合或解聚。第一种正作用光刻胶是酚醛和重醌(DNQ)光活性溶解抑制剂,由德国Kalle and Company, AG及其美国子公司Azoplate Corporation于20世纪20年代初开发。抗蚀剂的选择取决于分辨率、成本、加工难易程度等因素。由于负型抗蚀剂具有高分辨率和广泛的易加工性,因此被用于IBM先进设备CMOS逻辑器件的图案化。

Photo-polymerization properties of type-II photoinitiator systems based on 2-chlorohexaaryl biimidazole (o-Cl-HABI) and various N -phenylglycine (NPG) derivatives. Photochem. Photobiol. Sci. 2019

20世纪70年代初,上述KTFR等负性抗蚀剂无法满足半导体工业的分辨率要求。因此,基于重氮化学的新型正极材料应运而生,它具有许多优点。

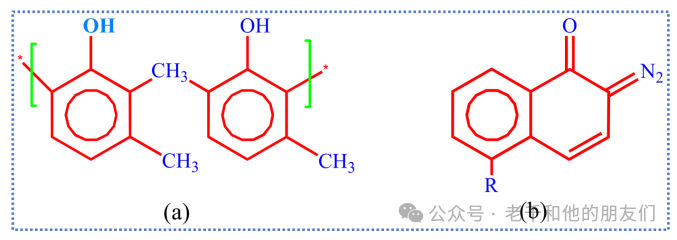

图 3. 大多数商业 i-line 光刻胶使用的 (a) 酚醛聚合物和 (b) 重醌类光活性化合物的化学结构。

MacDonald, S.A.; Frechet, J.M.J.; Ito, H.; Grant Willson, C. Resist materials. Microelectron. Eng. 1985

聚(4-叔丁氧羰基氧基苯乙烯)、tBOC 和三苯基锍六氟锑酸鎓盐是最早用作 DUV负阻系统的聚合物。20世纪80年代末,当 tBOC暴露在 DUV 光下时,它被用于制造1 Mb DRAM。当时安装了特殊的碳过滤器来保护 CAR 免受污染物的扩散。化学放大负阻剂(即酸催化 EPR 和 tBOC)均可用于制造 1 Mb 芯片,其图案为 1 µm 基本规则。

Ito, H. Chemical Amplification Resists: History and Development within IBM. IBM J. Res. Dev. 1997,

1 Shaw, J.M.; Gelorme, J.D.; LaBianca, N.C.; Conley, W.E.; Holmes, S.J. Negative photoresists for optical lithography. IBM J. Res. Dev. 1997

2 Zawadzka, A.; Paszkiewicz, R. Limitations of optical lithography on non-planar surfaces. Mater. Sci. Semicond. Process. 2022

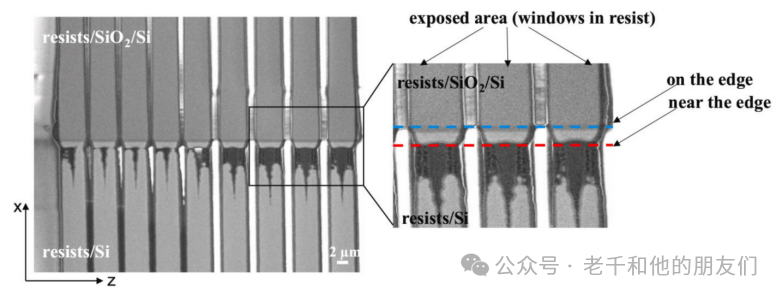

图 4. 显示二氧化硅阶梯边缘变形的 SEM 图像。

2.3光刻技术的局限性

Chopra, J. Analysis of Lithography Based Approaches in Development of Semiconductors. Int. J. Comput. Sci. Inf. Technol. 2014

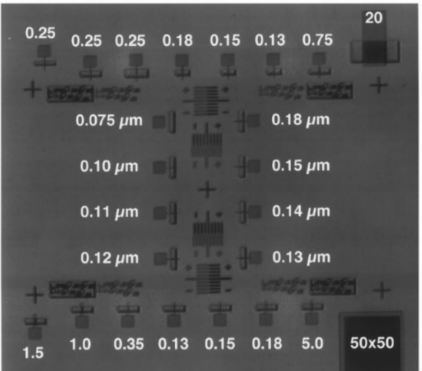

对于193 nm波长,光学光刻可达到0.13 µm,NA=0.65,K1=0.35。为了进一步提高分辨率,在投影光学器件和晶片之间的间隙中引入了浸入液体,从而提高了NA 值。目前,利用水浸ArF光刻技术,集成电路行业正处于以65纳米半间距制造45纳米节点的边缘。但浸入式光刻法也有局限性,即液体会产生气泡、留下应变和携带颗粒,从而在晶片上产生缺陷,这使得折射系统无法进行波长缩减,因此研究人员转而采用反射光学技术。

如果所有的扩展技术(即高折射率材料、掩膜上的固体浸渍和偏振照明)都取得成功,并在 1.55 NA 时支持K1=0.3,则半间距可达 37 nm。利用分割间距的趋势,将 k1 从 0.3 降低到 0.15,并建议半间距为19纳米。但是,分割间距技术的加工步骤、工具和掩膜都是双倍的,导致经济性降低。这就是为什么要引入其他光刻技术,如 EUVL、多电子束直接写入等。

3 极紫外光刻技术-EUVL(成都半导体微组装设备自动化)

光学光刻技术可用于100纳米以下的集成电路 (IC)。对于小于100纳米的半导体器件,则需要新一代光刻技术。极紫外光刻(EUVL)使用1988年提出的10-14 纳米极紫外光,可用于100纳米集成电路制造。预计极紫外光技术将扩展到30纳米以下。

自2018年起,EUVL已在半导体行业的大批量制造(HVM)中实施。在多重图案技术的帮助下,集成电路制造可以突破3纳米。EUVL 可用于 DRAM、MPU 和闪存(NAND)等器件的扩展。使用这种技术,NAND 闪存可缩小到 16 纳米。如图 5 所示,NMOS 晶体管由桑迪亚 EUVL 实验室工具制造,栅极长度为 1 µm。

1 EUV Lithography: State-of-the-Art Review. J. Microelectron. Manuf. 2019

2 Fabrication of metal–oxide–semiconductor devices with extreme ultraviolet lithography. J. Vac. Sci. Technol. B Microelectron. Nanom. Struct. 1996

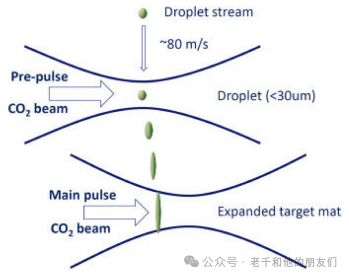

EUVL系统的主要组件包括曝光工具、聚光器多层反射镜、投射多层反射镜和掩膜。主要采用两种源概念:电(DPP)放电产生的等离子体源和(LPP)激光产生的等离子体源。

ASML’s a-Tool Development for EUVL; SPIE: Bellingham, WA, USA, 2002

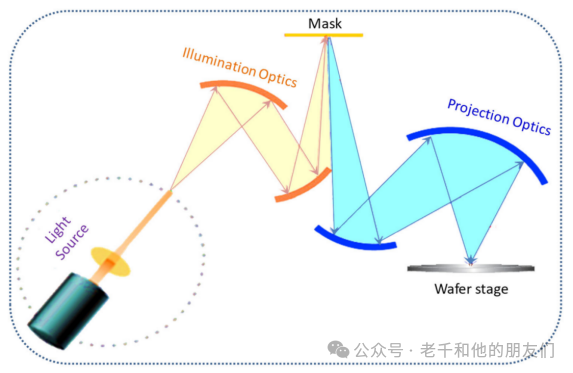

如图6所示,反射镜用于扫描仪的成像功能,而不是光学光刻中使用的折射透镜。这些反射镜由多达 100 层的硅或钼组成。对于波长为13.5 nm 的EUV,钼/硅层的厚度为0.75nm。这些反射镜通过干涉反射来自各层材料的光线。通过表面涂层,这些反射镜最多可反射落在其上的 72% 的极紫外光。其余的光会被镜子吸收。

Wagner, C.; Harned, N. EUV lithography: Lithography gets extreme. Nat. Photonics 2010

图 6. 极紫外激光技术的装置

The development of laser-produced plasma EUV light source. Chip 2022

图 7. 极紫外生成和目标形成视图

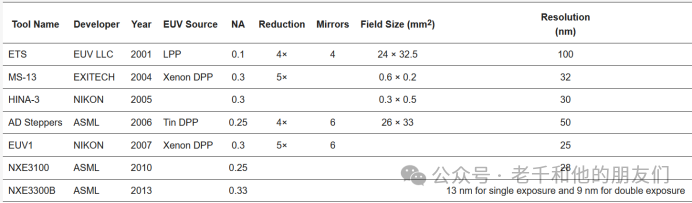

1997 年,EUVL预计在 65 纳米节点上实现,但光学光刻技术的进一步发展将 EUVL 的实现推到了 45 纳米节点之后。2001 年,EUV LLC 准备了全场曝光工具。它由一个步进扫描系统、四个反射镜和一个环形设计场组成。它的数值孔径为 0.1,缩小了四倍。该系统使用了 LLP EUV 光源。该工具的特征尺寸为 100 nm。该系统的 ETS 场尺寸为 24 × 32.5 mm2。微曝光步进器 (MS-13) 由 Exitech 于 2004 年开发。它的数值孔径为 0.3,缩小了 5 倍,磁场尺寸为 0.6 × 0.2 mm2 。

2005 年,尼康公司开发了 HINA-3,其数值孔径为 0.3,视场大小为 0.3 × 0.5 平方毫米。为了展示 EUVL 的进步,ASML 于 2006 年在美国和欧洲举办了阿尔法演示曝光工具。该工具使用了锡放电等离子体 (DPP) 光源。该系统有六个反射镜,四倍缩小,NA 为0.25。该工具的磁场尺寸为 26 × 33 平方毫米。该工具可实现 50 nm 的特征尺寸。NXE 3100 由 ASML于2010年开发。它的NA值为 0.25,分辨率为 28 纳米。但该工具的源功率为 10 W,因此吞吐量较低。

NXE 3300B 于 2013 年开发,数值孔径为 0.33。该工具可实现 13 纳米的分辨率,在双图案化的帮助下可实现 9 纳米的分辨率。

3.1 光刻胶

EUVL主要使用两类光刻胶:化学放大光刻胶和非化学放大光刻胶。下一代光刻抗蚀剂面临的主要挑战是分辨率、灵敏度和线边缘粗糙度(LER)。此外,除气、EUV 吸收和缺陷密度也会影响系统的生产率。化学放大光刻胶(CAR)通常用于 248 纳米和 193 纳米光学光刻。但在用于极紫外光刻时,化学放大抗蚀剂面临着一些限制,如 LER、超紫外吸收和图案塌陷。CAR 主要由光酸发生器(PAG)和聚合物组成。10 mJ/cm2 低曝光剂量的 EUV 光源需要高灵敏度和高 PAG 负载。要控制 32 纳米节点的比率方面,需要55-100 纳米厚的抗蚀剂。在图案转换过程中,薄型抗蚀剂需要具有高抗蚀性。

放气会干扰系统并缩短光学工具的使用寿命。EUVL工艺必须在高真空环境下进行,因此放气现象也会加剧。根据 ITRS 的数据,放气率为5 × 103个分子/平方厘米。非离子PAG和抗蚀剂具有高活化能,可用于减少放气。LER不仅对 EUVL 而且对所有下一代光刻技术来说都是一个巨大的挑战。248 纳米波长的光子能量为5eV,193纳米波长的光子能量为6eV。而13纳米波长的光子能量为 93eV。每个光子能量的增加导致了射出噪声和LER的增加。硬掩膜上的单层超薄抗蚀剂可用于控制 LER。还可以观察到,小尺寸PAG和高浓度 PAG可以降低LER 。

不同的抗蚀剂对EUV光的吸收不同。这取决于分子中的原子吸收。抗蚀剂材料可以由碳、氢和硅原子制成,以减少吸收。EUVL光刻胶中的硼原子也能减少吸收并增强抗蚀刻性。光刻胶基底的光密度约为4.0μm-1,透射率分别为67.0% 和 44.9%,对应的光刻胶厚度分别为100nm和200nm。建议成像层厚度为120± 15nm。一般认为,极紫外光子在抗蚀剂材料中产生的低能电子(LEEs)是导致纳米图案形成的溶解度变化的主要原因。

Key Role of Very Low Energy Electrons in Tin-Based Molecular Resists for Extreme Ultraviolet Nanolithography. ACS Appl. Mater. Interfaces 2020

3.3 光刻胶材料的进步

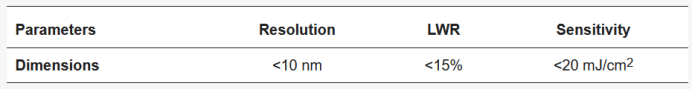

有关 EUVL 光刻胶的研究结果已在2007年的 SPIE 高级光刻会议上公布。工业应用光刻胶所需的参数如表2所示。XP6627 CAR 用于在 25 纳米节点上获得1:1的线条:空间特征分辨率。该系统的3σ LER 值较低,为2.7 nm。在取得这些结果之后,预计 EUVL CAR 可以扩展到22 nm节点。而由非离子 PAG 和聚合物组成的其他 CAR 可以扩展到 50 nm 以下的分辨率。在 50 纳米处观察到 1:1 的线:空间特征,在 20 纳米处观察到 1:4。

2007 年,分子光刻胶的灵敏度和 LER 在 EUVL 中得到了提高。12 mJ/cm2 的曝光剂量和 3.1 nm 的 LER 可用来打印 45 nm 以下的图案。ASML推出了曝光剂量为 40 mJ/cm2 的新工具,降低了13 nm节点 EUVL 光刻胶分辨率的难度。Nagahara等人引入了洪流曝光辅助化学梯度增强技术 (FACET),以提高抗蚀剂的粗糙度、分辨率和灵敏度。

Yamamoto 等人添加了金属敏化剂以提高 CAR 的灵敏度。由于酸产率提高,灵敏度也得到了改善,电子的效率也得到了提高。因此,灵敏度提高了 43%。这也有助于降低 LER。

Lee等人给出了一个多尺度模型,对CAR结构形成过程中发生的各种化学反应(如扩散、脱保护等)进行了内部研究。这种多尺度模型还可以预测聚合物损耗和 LER 性能。Brainard 等人开发并评估了11 种酸放大器(AA)。Brainard 使用 ESCAP 光刻胶来研究 AA 的影响。AA 产生了氟化磺酸。它有助于提高 EUVL 光刻胶的分辨率、LER 和灵敏度。Kudo 等人利用他们合成的 Noria 衍生物制作了 25 nm 节点的图案。他使用的曝光剂量小于10 mJ/cm2。

Kulshrestha等人开发了一种负色调 CAR。他们合成了具有氧杂环丁烷交联分子的 Noria 分子。这些改性提高了灵敏度、LER 和膨胀率。在 20 nm 节点上形成了 1:1 的线:空间图案,LER 为 3.2 nm。研究了分子量和加工参数对抗蚀剂功能性的影响。

3.4 掩膜

EUVL 掩膜基于 EUVL 空白掩膜制备技术和利用原材料制造掩膜的技术。制作掩膜需要热膨胀系数较低的基底。用原材料制作掩膜的过程包括以下步骤:生成图案、图案转移、控制质量和缺陷。EUV 掩膜的反射率为 65-70%。英特尔公司为实施 EUV 技术建立了一条 EUV 掩膜试验线。为了控制平面外位移(OPD),EUV 掩膜的基板必须平整。

20世纪90年代,极紫外光的预期实施范围是100纳米节点,但现在预计会扩展到32纳米和22纳米节点以上。为了通过极紫外光获得更高的分辨率,使用相移掩模技术在约100纳米处蚀刻了一个多层反射器。100 nm节点最初要求零缺陷,大于80 nm聚苯乙烯胶乳 (PSL) 等效尺寸。32 纳米节点的缺陷尺寸为 26 纳米 PSL 等效尺寸。32 nm节点要求正面和背面的峰谷平整度为32 nm,以便与静电吸盘正确接触。到2007年,峰谷平整度的目标有望达到 50 nm。正面 120 nm p-v 和背面198 nm p-v 的基底具有最佳的集成性能。热泳保护法被用来克服制作非粒子 EUV 掩膜的问题。氩气压力为 50-1600 mTorr,粒子大小为 65-300 nm。

3.5 掩膜的进步(四川有哪些半导体微组装设备厂家?)

在2000年之前,100 纳米节点需要 EUV 掩膜。缺陷规格为 0.01/cm2。缺陷检测阈值为50-80纳米。可见光检测工具用于检测大于 130 纳米的 0.1/cm2。到 2002 年,EUVL 技术已发展到 65 纳米。为了获得 60% 的掩膜坯成品率,对缺陷密度的要求是0.0025个缺陷/平方厘米,这一要求同时适用于掩膜基板和多层板。

此时,镀膜技术也取得了进展。大于 90 nm PSL 的缺陷水平达到了 0.05/cm2。预计到 2004 年,EUVL 将扩展到 45 纳米或 32 纳米节点以上。放电缺陷检测用于检测空白掩膜上的缺陷。它能检测出宽度为 70 nm、高度为 3.5 nm 的缺陷。当时还开发了多层镀膜方法。检测到尺寸大于 80 nm PSL 当量的颗粒的缺陷密度为 0.055 个/cm2。该方法检测到的最低缺陷密度为 0.005 个/平方厘米。

22 纳米节点的掩膜缺陷尺寸应控制在18纳米。为了提高缺陷检测的灵敏度,在 EUVL 空白掩膜中使用了放电检测方法。2004 年检测到的缺陷宽度为 50-65 nm,高度为 10-12 nm,捕获率超过 90%。2006 年,光电子发射显微镜被用于检测 EUVL 掩膜中的缺陷水平。通过使用这种技术,利用放电掩膜空白检测法检测到了 30-50 纳米的埋藏缺陷和 6 纳米高的相结构

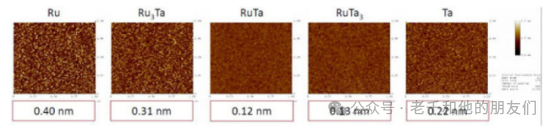

在电子束(e-beam)的帮助下,EUVL 掩膜制造技术不断发展。化学放大抗蚀剂(CAR)增强了图案生成过程。电子束对于提高光密度均匀性和光密度平均目标(MTT)并不重要。事实证明,一种被称为自掩膜的新型掩膜优于其他掩膜。这种掩膜可对吸收层进行多步蚀刻。热力学计算有助于选择化学体系,以确保自掩膜的功能。先进的建模和新的表征技术使掩膜的开发和加工变得更加容易。2021 年,开发了一种新的质量堆栈模型,其中包含多层 Mo/Si,再由Ru层和TaBN/TaBo 吸收层覆盖,这有助于模拟 EUVL 掩膜的性能。Ru4-xTax(x = 1、2、3)被认为是下一个候选的 EUV 低 n 掩膜,其原子力显微镜图像如图 8 所示。

图 8. 显示沉积在 30 纳米薄膜上的 Ru 和各种合金 RMS 值的原子力显微镜图像。

3.5 EUV光刻技术局限性

极紫外光刻面临着线边缘粗糙度(LER)和阻抗分辨率的挑战。对高真空环境的要求限制了 EUV 光刻技术的使用。它还面临着光刻胶脱气的问题。光刻胶对极紫外光的吸收和对光刻胶轮廓的影响是将极紫外光用于制造设备的困难所在。在用极紫外光替代193 纳米光刻技术之前,它必须解决许多关键挑战。要成为具有成本效益的技术,必须在晶圆级提高极紫外光的功率。

目前可用的EUV光源功率吞吐量不够高效。要集成功能集成电路,就必须降低反射掩膜上的缺陷密度。极紫外光掩膜图案的生成和传输是一项严峻的挑战。使用非微粒掩膜也是一项挑战。非微粒掩膜正逐渐被可移动微粒和热泳保护所取代。为了获得更高的分辨率、生产率并降低LER,需要对光刻胶进行改进。要使这项技术实用化,还需要取得很大进展。

更多的四川半导体微组装设备资讯请联系:18980821008(张生)19382102018(冯小姐)

四川省微电瑞芯科技有限公司http://www.wdrx-semi.com/