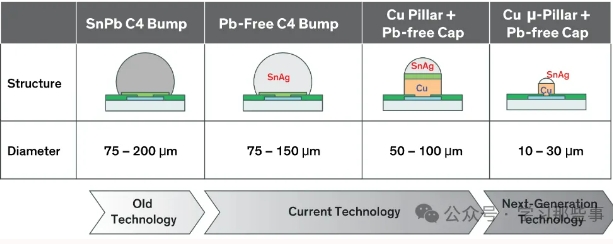

Cu-pillar是使用 TCFC(热压倒装芯片)技术将芯片倒装到封装(四川半导体封装设备有哪些?)基板上时使用的端子。Cu-pillar形成在芯片的铝电极焊盘上。由于芯片上集成的焊盘间距细小,引脚数增加,Cu-pillar互连的需求量也随之增加。

在晶圆端,相较于Solder Bump,Cu-pillar Bump具有Fine Pitch的优势,芯片尺寸可缩小约5~10%实现更小的封装结构,利用Fine Pitch及Bump on Trace制程,并采用简化基板制程,可将基板层数由6层减少至4层,因此基板成本可下降约30%。

它的优势有:

·细间距可达到30μm,TSV和CoC硅片封装间距极细,低至 30 μm

·出色的电迁移性能,适合高电流承载能力应用

·在铜柱凸块之前进行晶圆级电气测试

·能兼容专为引线键合而设计的芯片键合焊盘/间距和焊盘金属化,从而能够快速将芯片转换为倒装芯片

·通过减少基板层数,许多设计可以降低成本

·对于高凸块密度设计,与金柱凸块相比,细间距倒装芯片 (FPFC) 互连的成本更低

·提供各种铜柱结构,包括铜条类型、标准铜柱、细间距铜柱和微凸块。

·可提供重新钝化或不重新钝化

·符合先进硅节点 Low-k 器件的要求

·可实现更严格的芯片到封装(四川平行封焊机)设计规则/更小的封装尺寸

1.Cu-pillar Structure

2.Copper Pillar电镀工艺

免责声明:文章归原作者所有,转载仅为分享和学习使用,不做任何商业用途!内容如有侵权,请联系本部删除!小编:19181980439

更多的四川半导体微组装设备资讯请联系:18980821008(张生)19382102018(冯小姐)

四川省微电瑞芯科技有限公司http://www.wdrx-semi.com/